下一代存储材料

近年来,氧化物半导体作为下一代存储架构的潜力材料受到广泛关注,其关键优势在于可实现与后端互连工艺(BEOL)兼容的逻辑与存储器件。本文报道了基于氧化物半导体沟道的 BEOL 存储器件在近期取得的进展与面临的挑战,包括类 DRAM 的 1T-1C 存储单元、无电容增益单元以及非易失性铁电场效应晶体管(Ferroelectric FET)。文章分析了氧化物沟道的关键特性,重点关注在材料与器件工艺技术方面的进展,这些进展有助于提升存储器的核心指标,如耐久性、数据保持特性以及可扩展性。这些研究结果为优化基于氧化物半导体的存储器件、以满足下一代应用需求,提供了有价值的参考。

生成式人工智能应用(如大语言模型,LLMs)的迅速普及,引发了向以数据为中心的计算范式转变,并对新型存储技术提出了前所未有的需求。这些存储技术必须具备更高的容量和带宽,并在能效方面表现更优,以支撑日益复杂的工作负载。为应对这些挑战,氧化物半导体(OS)沟道材料正成为创新型存储单元设计的重要候选。这类设计旨在与现有存储解决方案(如 SRAM、DRAM)形成互补,通过实现与 BEOL 兼容的存储架构,推动存储系统层级结构的变革。值得注意的是,基于氧化物半导体的存储器具备独特特性,例如单元覆盖外设(Cell-over-Peripheral,COP)设计,这得益于其与先进 CMOS 逻辑器件的单片集成能力。

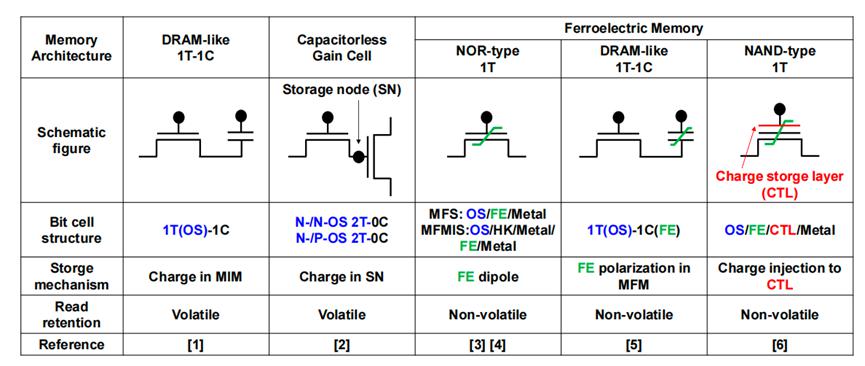

在 n 型氧化物半导体方面已取得显著进展,包括 IGZO、InWO、InSnO 以及 InO 等材料。由于其超低漏电特性以及与低于 400 ℃ 的低热预算工艺兼容,这些材料已成为 BEOL 存储单元接入晶体管的自然选择。然而,寻找性能可与之匹配的 p 型氧化物沟道材料仍然更具挑战性。该方向目前仍是一个活跃的研究领域,并且与 n 型氧化物半导体相结合,有望推动远超存储系统本身的新型应用。表 I 总结了当前正在密集研究的三类主要 BEOL 兼容、基于氧化物半导体沟道的存储器类型:

表 I: 基于氧化物半导体(OS)沟道的主要 BEOL 兼容存储器总结

(1)采用超低漏电 n 型氧化物半导体接入晶体管的类 DRAM 1T-1C 存储结构;

(2)由 n 型与 p 型氧化物半导体晶体管组成的无电容增益单元存储器,其结构形式包括 2T-0C 或 nT-0C;

(3)将 n 型氧化物半导体沟道与基于 Hf 的铁电介质相结合,构成铁电场效应晶体管

在本文中,我们将回顾基于氧化物半导体(OS)的存储单元技术的最新进展,并讨论为满足性能需求,在材料与器件开发方面所取得的进展与面临的挑战。通过探讨 n 型与 p 型氧化物沟道,我们旨在为新兴存储架构中影响器件设计、可扩展性和可靠性的关键因素提供参考。

近期,在先进逻辑平台上展示了一种采用 n 型氧化物半导体晶体管的 1T-1C 存储芯片,其在制造工艺与晶圆厂兼容性方面表现出高度成熟性,并实现了优异的性能(见图 1 ( a ) )。该芯片在 0.75 V 的 VDD 条件下实现了 8 ns 的随机周期时间和 128 ms 的保持时间,并在 85 ℃ 条件下展现出多年级别的可靠性(见图 1 ( b ) )。整个存储单元阵列以 COP 结构单片集成在 CMOS 外围电路之上,通过最小化信号传播距离,在密度扩展以及延迟和功耗降低方面提供了显著优势。n 型氧化物半导体材料已被广泛研究,其成熟度在实现这一突破中发挥了关键作用。

图 1:(a)采用 COP 结构的 BEOL 1T-1C 存储器的截面 TEM 图;(b)1T-1C 存储芯片的 Shmoo 图,显示出良好的性能裕量。

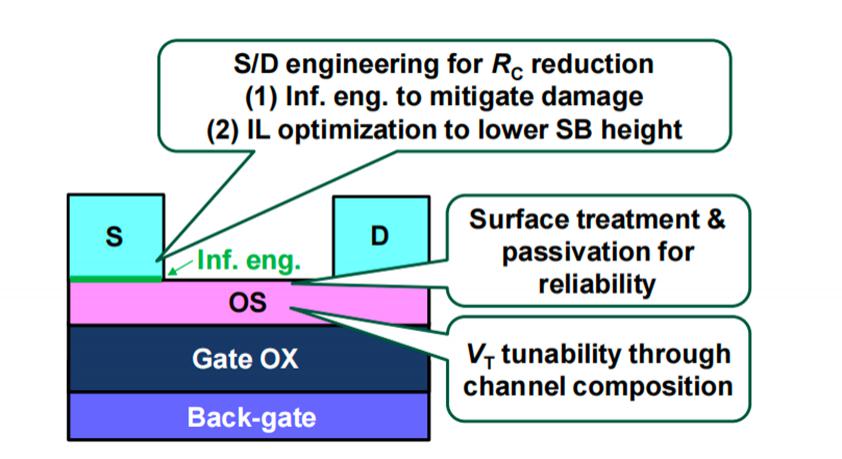

然而,要满足严苛的性能与可靠性要求,仍需解决若干关键挑战:(1)在短沟道(LG < 30 nm)器件中通过接触电阻(RC)优化实现高驱动电流(ION),以支持超低电压(< 0.75 V)运行从而降低功耗;(2)阈值电压(VT)调控,在抑制漏电的同时保持稳健的电路功能;以及(3)工艺与钝化控制,以降低 VT 波动并提升可靠性。图 2 给出了用于优化 n 型 OS 晶体管性能的策略示意图。

图 2: 用于优化 n 型 OS 晶体管性能的策略示意图。

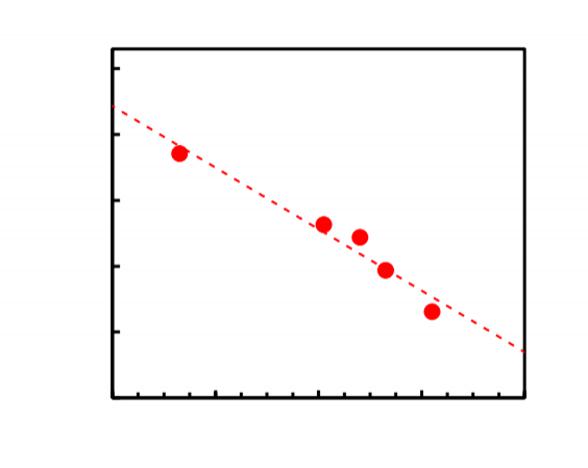

在尺寸缩小的 n 型 OS 器件中,降低接触电阻(RC)对于提升 ION 至关重要。图 3 ( a ) 对比了 RC 优化前后的 ID – VG 特性,其中优化措施包括:(1)通过接触工艺工程手段,减轻接触刻蚀过程中造成的表面损伤;(2)通过接触中间层(IL)优化,降低金属 / 半导体肖特基势垒(SB)高度。通过结合这些方法,实现了低于 500 Ω · μm 的 RC 值(见图 3 ( b ) )。

图 3:(a)进行接触电阻(RC)优化前后的 ID – VG 特性对比;(b)通过 TLM 方法提取的 RC 数值,显示经优化后 RC 低于 500 Ω · μm。

与硅基晶体管不同,基于氧化物半导体的晶体管在 VT 调控及其波动控制方面需要采用根本不同的方法,这涉及对 OS 沟道中金属离子浓度、氧空位以及氢含量之间微妙平衡的精确调控。图 4 展示了通过精确控制沟道成分实现的 OS 晶体管 VT 的宽范围可调性。然而,这类方法往往在 VT 与 ION 之间引入不理想的权衡关系,因此仍需在材料与工艺优化方面开展持续研究,以解决这一问题。

图 4: 通过精确控制氧化物半导体(OS)沟道成分实现的 VT 可调性,揭示了 VT 与 ION 之间的典型权衡关系。

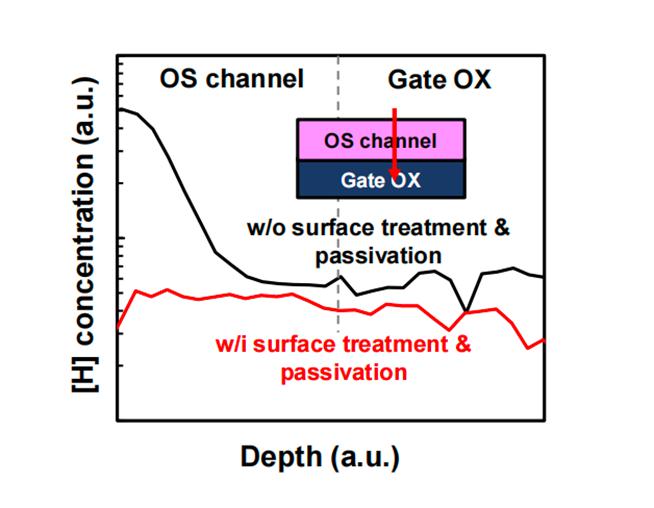

可靠性性能(包括正偏压温度不稳定性和负偏压温度不稳定性,PBTI/NBTI)对 OS 沟道晶体管中氢的存在高度敏感。已有研究表明,由于氢扩散和缺陷形成,n 型 OS 系统中会出现复杂的 PBTI 和 NBTI 行为。为减轻这些影响,采用了表面处理和钝化方法,以尽量减少氢含量并防止其在工艺过程中向沟道中扩散,如图 5 所示。

图 5: OS 沟道的 SIMS 深度剖面,显示通过表面处理与钝化有效降低了沟道中的氢含量。

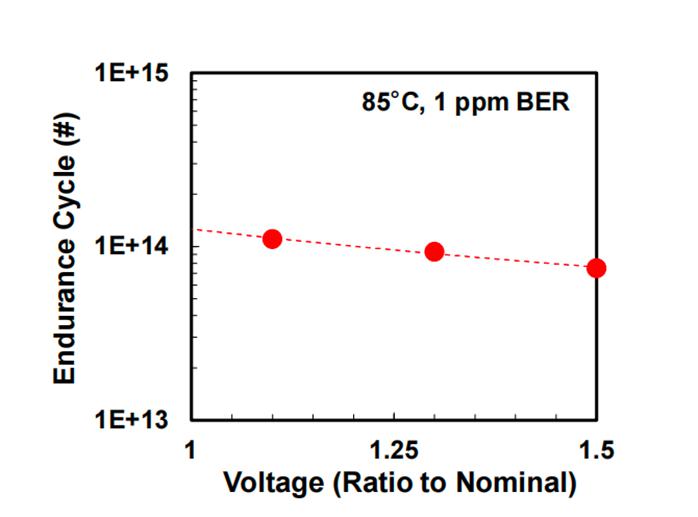

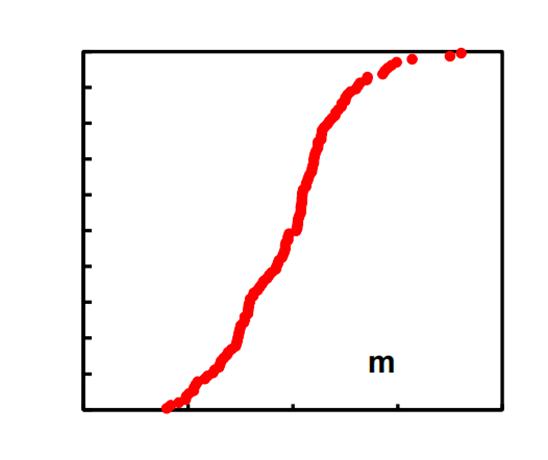

图 6 给出了采用优化工艺流程制备的 1T-1C 存储芯片的耐久性测试结果,在 85 ℃ 条件下经过 10¹ ⁴ 次循环后,其误码率(BER)仍低于 1 ppm。图 7 展示了在 25 ℃ 下优化后的 n 型 OS 器件性能,以及 VT 和 ION 的累积分布曲线,验证了该工艺在整片晶圆范围内具有较小芯片间差异的稳健性。性能基准结果如表 II 所示,在最短栅长(LG < 30 nm)条件下,实现了正 VT 条件下的最高 ION。

图 6: 1T-1C 存储芯片的耐久性测试结果,在 85 ℃ 条件下经过 10¹ ⁴ 次循环后,误码率(BER)仍低于 1 ppm。

图 7: 300 mm 晶圆上优化 n 型 OS 器件阈值电压(VT)的累积分布。

无电容 2T-0C 增益单元(GC)由一个写晶体管和一个读晶体管构成,可实现非破坏性读出,是高密度片上存储应用中一种具有前景的方案。基于氧化物半导体(OS)的增益单元已在 n – n 和 n – p 两种配置中得到验证。2T-0C 增益单元的工作主要由写 / 读晶体管之间存储节点(SN)处存储的电荷决定,并且对写字线(WWL)与 SN 之间的电容耦合尤为敏感。n 型 OS 晶体管的超低漏电特性使其成为理想的写晶体管候选,因为在待机状态下能够有效保持 SN 处的电荷。另一方面,由于电容耦合效应较弱,p 型沟道相较于 n 型沟道更适合作为读晶体管,从而为读操作提供更大的感测窗口。

尽管 n 型 OS 技术相对成熟,但 p 型 OS 材料的研究进展仍然有限且具有挑战性。近年来,一氧化锡(SnO)因其良好的热兼容性(可达约 350 ℃)、对氢的耐受性以及独特的电子结构而成为研究较多的 p 型氧化物半导体候选材料。在该材料中,价带由 O-2p 与 Sn-5s 轨道的重叠所形成,从而支持 p 型输运。然而,要在增益单元应用中充分实现 SnO 作为读晶体管的潜力,仍需解决若干挑战,包括:(1)提升迁移率并降低接触电阻以改善导通电流;(2)减小迟滞以实现稳定的阈值电压;以及(3)实现可调阈值电压和更高的 ION/IOFF 比,以降低漏电流和潜通路电流,这对于扩展存储阵列、在每条位线上集成更多单元至关重要。此前的概念验证研究已成功展示了通过物理气相沉积(PVD)制备的背栅 SnO 晶体管,其器件制备流程为实验室尺度。图 8 ( a ) – ( d ) 展示了典型 SnO 器件的 ID – VG 曲线、GI-XRD 以及 TEM 结果,表明器件具有良好的结晶质量,提取的迁移率约为 2 cm²/V · s。

在此基础上,本文进一步报告了采用晶圆厂兼容工艺流程制备 SnO 器件的最新成果。图 9 ( a ) 显示了在 300 mm 晶圆工艺中制备的长沟道(LG = 1 μm)SnO 器件的 ID – VG 曲线,其 ION/IOFF 比约为 10 ⁴,迁移率约为 1 cm²/V · s,迟滞小于 500 mV。这些器件采用背栅工艺制备,首先在晶圆上沉积金属作为背栅,其后通过 ALD 沉积高介电常数介质,再通过 PVD 沉积 SnO。在通过有源刻蚀定义并隔离沟道区域之后,沉积一层 SiO ₂ 作为层间介质(ILD)。

表 II: 1T OS 器件的性能基准对比。

最后,通过在 ILD 中进行接触刻蚀、金属填充以及化学机械抛光(CMP)形成源 / 漏(S/D)接触。值得注意的是,这些器件在 300 mm 晶圆范围内表现出良好的均匀性(见图 9 ( b ) )。尽管取得了这些积极进展,仍需在材料与工艺开发方面进行进一步探索和优化,以充分释放基于 SnO 器件的潜力。

通过 PVD 制备 SnO 的沉积参数(如氧分压 Opp% 以及总压强)对于抑制不期望的锡氧化态(如 Sn 或 SnO ₂)的形成至关重要,这些相的存在可能导致不利的金属性或 n 型输运行为。图 10 展示了在不同 Opp% 和总压强条件下 SnO 晶体管的 VT – ION 关系,表明这些参数对薄膜质量和器件行为具有显著影响。结果表明,SnO 中可能存在渗流输运现象,这种现象在 n 型 OS 中也较为常见,但仍需进一步研究以全面阐明该材料体系中的主导输运机制。针对 p 型 OS 晶体管的源 / 漏接触优化采用了两种方法:(1)通过降低接触 /SnO 界面处的表面陷阱态密度,从而降低肖特基势垒(SB)高度;(2)提高源 / 漏区域的局部载流子浓度,以改善能带弯曲并减小隧穿宽度。图 11 展示了接触电阻随栅极电压显著调制的行为,反映了肖特基接触的特性。通过接触优化,实现了约 5 倍的 RC 降低。

采用 Hf ₁₋ₓ Zr ₓ O 作为铁电层的铁电场效应晶体管(FeFET),由于其基于电场驱动的写入机制,被认为是实现高速、低功耗存储的有前景候选方案。氧化物半导体沟道与铁电介质均可采用 ALD 工艺沉积,这为实现高密度、具备优异成本可扩展性的三维存储提供了可行性。然而,将铁电材料与氧化物半导体沟道进行集成,会为 OS-FeFET 存储器的运行引入一些独特挑战。主要问题包括:(1)由于 n 型 OS 沟道中空穴载流子不足而导致的弱擦除现象;以及(2)由氧化物半导体沟道中氧空位的生成及其向铁电层扩散所引起的耐久性退化。

近期,通过展示一种高度缩放的 OS-FeFET 存储器件,在该领域取得了重要突破,该器件的单元面积为 0.009 μm²。该器件采用 n 型 OS 沟道,在 300 mm 晶圆上制备,实现了 40 μA/μm 的导通电流、30 ns 的高速操作、在 85 ℃ 条件下超过 1000 s 的数据保持能力,以及 10¹² 次循环的耐久性(见图 12)。这一成果得益于多项关键工程策略,包括:(1)通过调节 Zr 含量实现 HZO 相结构优化(见图 13);(2)通过协同优化铁电层与 OS 沟道的厚度及成分实现阈值电压调控(见图 14);(3)通过 OS/ 铁电界面工程抑制氧空位的产生,并通过优化厚度以降低硬击穿风险(见图 15);以及(4)在 HZO 中引入掺杂以抑制氧空位扩散(见图 16)。基于 OS-FeFET 存储器的非易失性及电场驱动机制,还可通过实现每比特多电平操作来进一步提升存储密度。然而,这将需要显著改善器件的离散性和均匀性,以确保大规模阵列中的一致性能。

基于氧化物半导体(OS)的存储技术为重塑存储系统层级结构提供了重要机遇,并有望实现高密度、高能效的系统,以满足不断增长的数据中心型工作负载需求。基于 n 型 OS 的新型存储架构已取得显著进展。然而,要充分释放 OS 技术的全部潜力,仍需在 p 型 OS 材料研究方面实现关键性突破,这将进一步拓展下一代存储与逻辑解决方案的应用范围。